# 3-Bit Programmable Analog Delay Line

The 3-Bit Programmable Analog Delay Lines manufactured by Engineered Components Company are designed to provide precise and stable delays for analog delay line applications. These delay lines are digitally programmable by the presence of either a TTL "high" or a TTL "low" at each programming pin to allow for final delay adjustment during or after installation in a circuit. Programming may be accomplished in 8 equal delay steps by remote switching or by permanent termination of the appropriate programming pins. Vcc (+5V typical) and Vee (-5V typical) are required for proper operation of the digital controls. The enable pin should be connected to a TTL "low" during normal operation. When the enable pin is high, the outputs are disabled to a high impedance "off" state.

The MTBF on these delay lines, when calculated per MIL-HDBK-217, for a 50 deg.C ground fixed environment and with 50VDC applied, is in excess of 1.6 million hours. The temperature coefficient of delay is less than 100 ppm/deg.C over the operating temperature range of -40 to +85 deg. C.

The delay line is provided in a 14-pin DIP package, fully encapsulated in epoxy resin and is housed in a Diallyl Phthalate case, green in color. The case marking is applied by silkscreen using white epoxy paint. The 9 copper leads are tin-lead plated and meet the solderability requirements of MIL-STD-202, Method 208.

## **Operating Specifications:**

All measurements made at 25 deg. C

All measurements made with Vcc = +5VDC

All measurements made with Vec = -5VDC

All measurements made with a 10 Mhz sine wave

All measurements made with a 100K ohms output load

Delays measured at 50% level on the leading edge

Input Impedance is 100 ohms +/-10%

Output Impedance is 170 ohms typical

Supply current < 1mA typical

Multiplexer setup time is 24 ns typical

Operating Temperature: -40 to +85 deg. C

Storage Temperature: -55 to +125 deg. C

Analog Input voltages should not exceed the Vcc supply

Analog Input voltages should not exceed the Vee supply

Programming and Enable pins: "Low" level input voltage: 2.0V min. "High" level input voltage: 0.8V max. Input Leakage current: 1uA max.

# MECHANICAL DIAGRAM .060 TYP. .300 TYP. .3

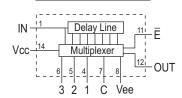

### **BLOCK DIAGRAM**

| <b>TRUTH TABLE</b>  |   |      |        |  |  |  |  |  |

|---------------------|---|------|--------|--|--|--|--|--|

| Example: PADL-1-1.0 |   |      |        |  |  |  |  |  |

| Pro                 |   | Pins | Output |  |  |  |  |  |

| 3                   | 2 | 1    | Delay  |  |  |  |  |  |

| 0                   | 0 | 0    | *1.0   |  |  |  |  |  |

| 0                   | 0 | 1    | **1.0  |  |  |  |  |  |

| 0                   | 1 | 0    | **2.0  |  |  |  |  |  |

| 0                   | 1 | 1    | **3.0  |  |  |  |  |  |

| 1                   | 0 | 0    | **4.0  |  |  |  |  |  |

| 1                   | 0 | 1    | **5.0  |  |  |  |  |  |

| 1                   | 1 | 0    | **6.0  |  |  |  |  |  |

| 1                   | 1 | 1    | **7.0  |  |  |  |  |  |

## **Product Selection Table**

| 1 Todact Sciection Table |                 |                 |              |                       |                |  |  |  |  |

|--------------------------|-----------------|-----------------|--------------|-----------------------|----------------|--|--|--|--|

| Part                     | *Step Zero      | Nominal Maximum | Delay Change | **Maximum Deviation   | -3dB Bandwidth |  |  |  |  |

| Number                   | Delay Time (nS) | Delay Time (nS) | Per Step     | From Programmed Delay | (in MHz)       |  |  |  |  |

| PADL-1-0.5               | 1.0+/-0.5       | 4.5             | 0.5+/-0.3    | +/-0.4                | 45.0           |  |  |  |  |

| PADL-1-1.0               | 1.0+/-0.5       | 8.0             | 1.0+/-0.3    | +/-0.4                | 30.0           |  |  |  |  |

| PADL-1-1.5               | 1.0+/-0.5       | 11.5            | 1.5+/-0.4    | +/-0.5                | 25.0           |  |  |  |  |

| PADL-1-2.0               | 1.0+/-0.5       | 15.0            | 2.0+/-0.4    | +/-0.6                | 20.0           |  |  |  |  |

| PADL-1-2.5               | 1.0+/-0.5       | 18.5            | 2.5+/-0.4    | +/-0.7                | 17.0           |  |  |  |  |

| PADL-1-3.0               | 1.0+/-0.5       | 22.0            | 3.0+/-0.5    | +/-0.8                | 13.5           |  |  |  |  |

| PADL-1-3.5               | 1.0+/-0.5       | 25.5            | 3.5+/-0.5    | +/-0.9                | 12.0           |  |  |  |  |

| PADL-1-4.0               | 1.0+/-0.5       | 29.0            | 4.0+/-0.5    | +/-0.9                | 11.0           |  |  |  |  |

| PADL-1-4.5               | 1.0+/-0.5       | 32.5            | 4.5+/-0.5    | +/-1.0                | 10.5           |  |  |  |  |

| PADL-1-5.0               | 1.0+/-0.5       | 36.0            | 5.0+/-0.5    | +/-1.0                | 10.0           |  |  |  |  |

<sup>\*</sup>Step zero is referenced to the input pin.

Special modules can often be manufactured to provide for customer specific applications.

engineered components company

Phone: 805-369-0034 Fax: 805-369-0033 Web: www.ec2.com

<sup>\*\*</sup>Delay times after step zero are referenced to step zero.