# Dual 100K ECL Logic Delay Line

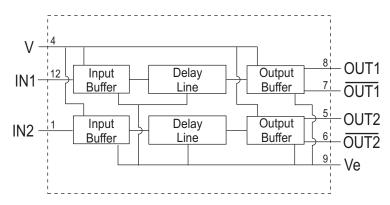

The Dual 100K ECL Logic Delay Lines manufactured by Engineered Components Company are designed to provide an output waveform that reproduces the input waveform after a set amount of delay time has elapsed. These delay lines provide both inverting and non-inverting outputs. The delay times are calibrated to the listed tolerances on the rising edge delays at the non-inverting outputs. Each module consists of 2 separate delay lines, each isolated and individually buffered.

The MTBF on these modules, when calculated per MIL-HDBK-217, for a 50 deg.C ground fixed environment and with 50VDC applied, is in excess of 1.0 million hours. The temperature coefficient of delay is less than 150 ppm/deg.C over the operating temperature range of 0 to +85 deg. C.

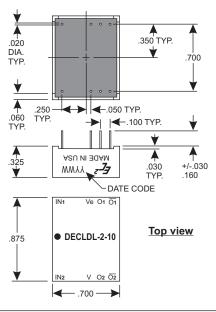

The module is provided in a 12-pin DIP package, fully encapsulated in epoxy resin and is housed in a Diallyl Phthalate case, blue in color. The case marking is applied by silkscreen using white epoxy paint. The 8 copper leads are tin-lead plated and meet the solderability requirements of MIL-STD-202, Method 208.

#### **BLOCK DIAGRAM**

| Product Selection Table |                   |

|-------------------------|-------------------|

| Part                    | Output Delay and  |

| Number                  | Tolerance (in ns) |

| DECLDL-2-2              | 2.0+/-0.2         |

| DECLDL-2-2.5            | 2.5+/-0.2         |

| DECLDL-2-3              | 3.0+/-0.3         |

| DECLDL-2-3.5            | 3.5+/-0.3         |

| DECLDL-2-4              | 4.0+/-0.4         |

| DECLDL-2-4.5            | 4.5+/-0.4         |

| DECLDL-2-5              | 5.0+/-0.5         |

| DECLDL-2-5.5            | 5.5+/-0.5         |

| DECLDL-2-6              | 6.0+/-0.6         |

| DECLDL-2-6.5            | 6.5+/-0.6         |

| DECLDL-2-7              | 7.0+/-0.7         |

| DECLDL-2-7.5            | 7.5+/-0.7         |

| DECLDL-2-8              | 8.0+/-0.8         |

| DECLDL-2-8.5            | 8.5+/-0.8         |

| DECLDL-2-9              | 9.0+/-0.9         |

| DECLDL-2-9.5            | 9.5+/-0.9         |

|                         |                   |

Product Selection Table (Cont.)

| A                 |

|-------------------|

| Output Delay and  |

| Tolerance (in ns) |

| 10.0+/-1.0        |

| 10.5+/-1.0        |

| 11.0+/-1.0        |

| 11.5+/-1.0        |

| 12.0+/-1.0        |

| 12.5+/-1.0        |

| 13.0+/-1.0        |

| 13.5+/-1.0        |

| 14.0+/-1.0        |

| 14.5+/-1.0        |

| 15.0+/-1.0        |

| 16.0+/-1.0        |

| 17.0+/-1.0        |

| 18.0+/-1.0        |

| 19.0+/-1.0        |

| 20.0+/-1.0        |

|                   |

Special modules can often be manufactured to provide for customer specific applications.

### **MECHANICAL DIAGRAM**

#### **Operating Specifications:**

All measurements made at 25 deg. C

All measurements made with Vee = -4.5VDC, Vcc = 0VDC All measurements made with (1) 100K ECL output load All measurements made with a 50 ohm pulldown resistor to -2VDC at the input and output

Operating Temperature: 0 to +85 deg. C Storage Temperature: -55 to +125 deg. C

Vcc Supply Voltage: -4.5 +/-5% VDC Vee Supply Current: 155mA typical Logic "High" Input:

Voltage: -1.165VDC min. Current: 350uA max. Logic "Low" Input:

Voltage: -1.475VDC max. Current: 0.5uA min.

Logic "High" Voltage Out: -1.025VDC min. Logic "Low" Voltage Out: -1.620VDC max.

## engineered components company

A Division of Cornucopia Tool & Plastics, Inc. PO Box 1915, 448 Sherwood Rd., Paso Robles CA 93447

Phone: 805-369-0034 805-369-0033 Web: www.ec2.com